编辑推荐:

为解决量子比特控制接口的互连密度难题,悉尼大学等机构研究人员开展"芯片级"低温CMOS控制硅基自旋量子比特研究。通过异构集成105晶体管的28nm FDSOI控制芯片与量子器件,在保持单比特门保真度99.93%、两比特门相干时间20μs的同时,实现20nW/MHz的超低功耗控制,为百万级量子比特集成提供热噪声抑制解决方案。该成果发表于《Nature》,标志着硅基量子计算向实用化迈出关键一步。

量子计算面临的核心挑战在于如何协调量子比特的微观特性与宏观控制系统的矛盾。硅基自旋量子比特虽具有亚微米级尺寸和长相干时间优势,但传统控制方案需要为每个物理比特配置多条控制线,当扩展到百万比特规模时,将面临"布线危机"——仅控制线密度就足以阻碍系统扩展。更棘手的是,交换耦合两比特门对电压噪声极其敏感,而传统室温控制电子学产生的热负荷和电噪声会显著降低量子操作保真度。

为解决这一根本性矛盾,由悉尼大学领衔的国际团队创新性地提出异构集成的"芯片级"架构。研究人员将包含105个晶体管的28nm全耗尽绝缘体上硅(FDSOI)低温CMOS控制芯片与硅MOS量子器件共集成在毫开尔文温区,通过微型化互连实现紧密耦合。这种设计既保留了CMOS电路的高集成度优势,又通过物理分离降低了热噪声耦合,同时利用低温环境天然抑制晶体管的热噪声。

关键技术包括:1)采用32通道电荷锁定快速门(CLFG)电路,通过电容耦合机制产生100mV脉冲,功耗仅20nW/MHz;2)开发全局微波共振场控制方案,利用J栅极电压斯塔克(Stark)位移实现单微波频率多比特寻址;3)结合射频单电子晶体管(RF-SET)实现微秒级电荷态读取;4)在0.5T磁场下通过电子自旋共振(ESR)完成单比特操控。

研究团队通过系列实验验证了该架构的优越性:

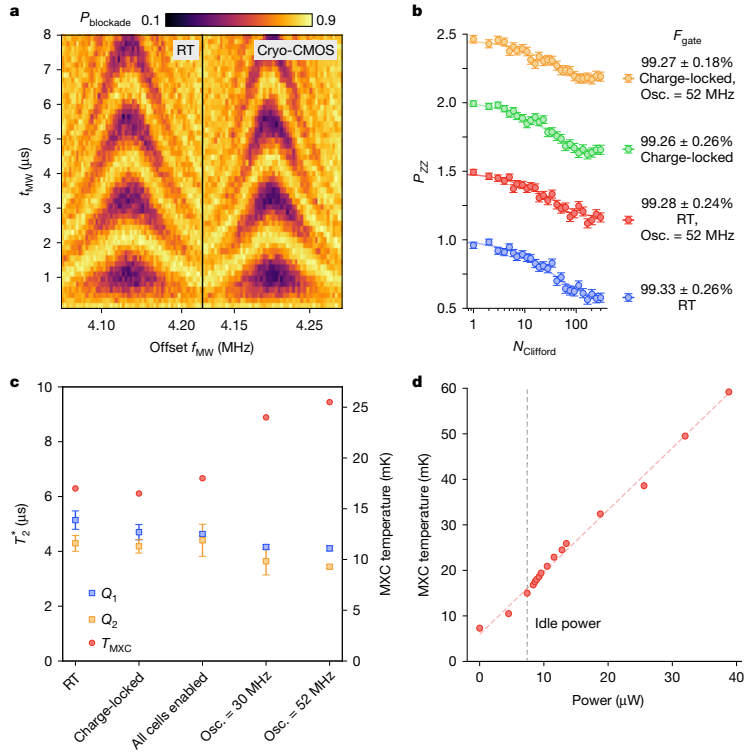

单比特门性能

在13.9GHz微波频率下,随机基准测试(RB)显示低温CMOS控制保真度达99.93%,仅比室温控制低0.07%。全局控制方案中,利用J栅极1MHz/10mV的斯塔克位移,实现了固定时间宽度的π/2脉冲操控,相干时间T2*保持15μs。值得注意的是,当CMOS芯片所有32个CLFG单元同时工作时,量子器件电子温度仅从850mK升至900mK,证明热管理有效性。

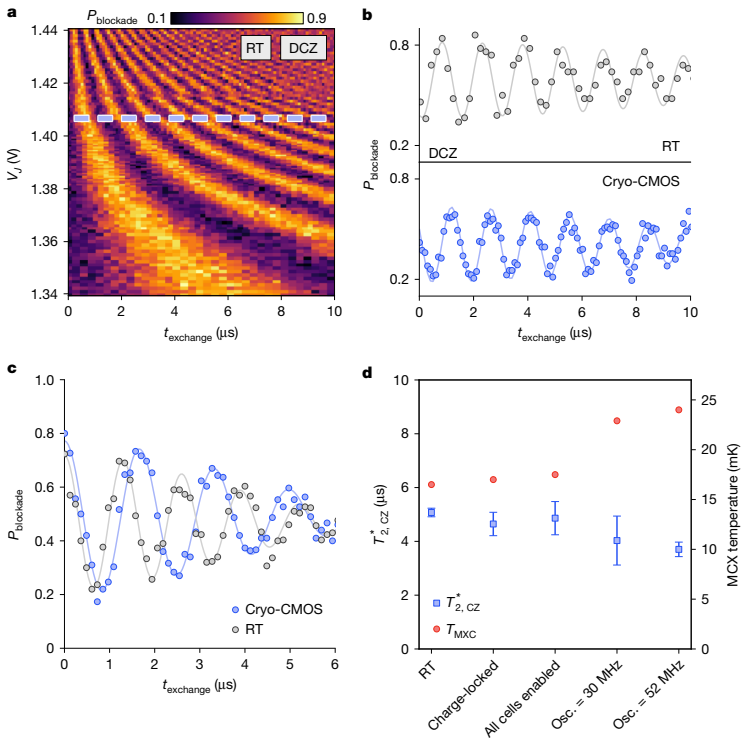

两比特门验证

交换耦合门(DCZ)作为对电噪声最敏感的指标,在低温CMOS控制下仍保持20μs的T2,exchange相干时间,仅比室温控制降低20%。通过自旋回波序列抑制低频噪声后,两比特门操作可见度与室温方案相当,证实CMOS开关瞬态噪声未引入额外退相干机制。

热噪声分析

通过CMOS环形振荡器主动加热实验证实,量子性能退化主要源于寄生热传导而非电噪声。当混合室温度从7mK升至1K时,量子器件电子温度呈线性增长,但T2*仅下降30%,表明硅自旋比特具有良好高温稳定性。噪声谱分析显示,CMOS工作未引入特定频率噪声尖峰,仅表现为宽频热噪声基底抬升。

该研究突破了量子控制系统的密度-噪声-功耗"不可能三角",其科学价值体现在三方面:首先,实验验证了异构集成架构的热力学可行性,105晶体管CMOS与量子器件的共存为后续扩展奠定基础;其次,提出的全局微波+基带脉冲控制范式,将外接微波源数量从O(N)降至O(1),极大简化系统复杂度;最后,发现的低温CMOS噪声特性表明,通过优化封装热阻和互连带宽,有望实现更低噪声的控制方案。

正如作者David J. Reilly强调的,这项工作不仅解决了硅基量子比特的控制瓶颈,其"芯片级"集成理念更可推广至半导体量子点、超导比特等多种平台。随着300mm硅工艺中量子器件制备技术的成熟,这种CMOS兼容的控制架构或将成为实用化量子处理器的主流技术路线。

生物通 版权所有